Volume 7, 2025 3DInCites.com

Page 9

Technical Features

Page 40 2025 3D InCites Awards Finalists **Page 52**The Year in Pictures

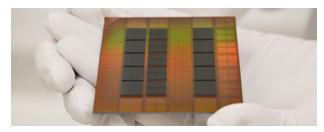

## FUSION AND HYBRID BONDING FOR HETEROGENEOUS INTEGRATION

### Enabling advanced 3D device stacking and chiplet integration for CMOS image sensors, memory and 3D system-on-chip (SoC) High-volume production equipment and process technology for Wafer-to-Wafer (W2W) and Die-to-Wafer (D2W) hybrid bonding GEMINI® FB Automated Production Wafer Bonding System delivers industry leading alignment accuracy and bonding performance Heterogeneous Integration Competence Center™ serving as leadingedge innovation incubator for EVG customers and partners **GET IN TOUCH** to discuss your manufacturing needs www.EVGroup.com

## CONTENTS

| 4        | Contributing Authors                                                                                                                            |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 7        | Editorial: Interconnectology Saves the World!                                                                                                   |

| 9        | TECHNICAL FEATURESCost-effective, High-performance Chips Are Driving the Move to Panel-level Processir By Jim Straus, ACM Research              |

| IU<br>10 |                                                                                                                                                 |

| 13       |                                                                                                                                                 |

| 16       | SPECIAL COVER SECTION                                                                                                                           |

| 17       |                                                                                                                                                 |

| 20       | 2024: A Year of Growth and Innovation By Peter Dijkstra, Trymax Semiconductors                                                                  |

| 23       | Empowering the Future: New York's Semiconductor Surge in 2024  By Scott Sikorski, Ph.D., IBM                                                    |

| 24       | Advanced Packaging in Asia  By Dean Freeman, Freeman Technology and Market Advisors                                                             |

| 27       | US-JOINT Consortium: Strengthening Semiconductor Innovation Across Borders By Avery Gerber                                                      |

| 29       |                                                                                                                                                 |

| 33       | The "White House of Microelectronics Packaging" Celebrates its 15th Anniversary!  By Juliana Panchenko and Frank Windrich, Fraunhofer IZM-ASSID |

| 34       |                                                                                                                                                 |

| 37       | Picking up the Pace of Panel-level Advanced Packaging at Onto Innovation  By Françoise von Trapp                                                |

| ŀO       | SPECIAL SECTION2025 3D InCites Awards Finalists Summarized by Avery Gerber                                                                      |

| 40       | Technology Enablement Awards                                                                                                                    |

| 43       | Engineer of the Year                                                                                                                            |

| 44       | Best Place To Work                                                                                                                              |

#### **CONTENTS CONTINUED**

| From Words to a World of Chips: My Experience with IMAPS and                  |

|-------------------------------------------------------------------------------|

| The International Symposium                                                   |

| By Camden McCrea, Texas A&M                                                   |

| Bridging the Semiconductor Talent Gap -                                       |

| The Role of the European Chips Act and Beyond                                 |

| By Isabella Drolz, Comet Yxlon                                                |

| Face It: Live Events Strengthen Partnerships and Influence Product Innovation |

| By Ramachandran (Ram) Trichur, Henkel Semiconductor Packaging Materials       |

| 2024 In Pictures                                                              |

| 2024 III Fictures                                                             |

| Ad Index                                                                      |

|                                                                               |

#### **STAFF**

#### Françoise von Trapp Publisher and Editor-in-Chief

Francoise@3DInCites.com Ph: 978.340.0773

#### Jillian McNichol Managing Editor

jmc@3DInCites.com Ph: 602.402.2408

#### **Stephen Wood Director of Operations**

stephen@3DInCites.com

#### Steffen Kröhnert Global Sales

steffen.kroehnert@espat-consulting.com Ph: +49 172 7201 472

#### **Phil Garrou**

Contributing Editor

PhilGarrou@att.net

#### Dean Freeman Contributing Editor

freconsult@gmail.com

#### Julia Freer Contributing Editor julia@jlfgoldstein.com

#### **Editorial Assistant Sarah Wood**

Sarah@3DInCites.com

#### **Editorial Intern Avery Gerber**

averygerber@tamu.edu

#### Creative/Production/Online

#### **Scott Timms**

Lead Designer

#### Ale Moreno

Web Developer

#### **Member Advisory Board**

**Dean Freeman**

FTMA

#### Dr. Phil Garrou

Microelectronic Consultants of NC, USA

#### Julia Freer

JLFG Communications, LLC

#### Steffen Kröhnert

**ESPAT-Consulting**

#### Manuela Junghähnel

Fraunhofer IZM-ASSID

#### Beth Keser

International Microelectronics and Packaging Society

#### Clemens Schütte

EV Group

#### E. Jan Vardaman

TechSearch International, Inc.

#### Subscribe to our e-newsletter, 3D InCites In Review: <a href="https://www.3dincites.com">https://www.3dincites.com</a>

The 3D InCites Yearbook is published by: 3D InCites, LLC

45 West Jefferson St. Suite 700

Phoenix, AZ, 85003 Ph: 978-340-0773

Copyright ©2025 by 3D InCites, LLC. All rights reserved. Printed in the U.S.

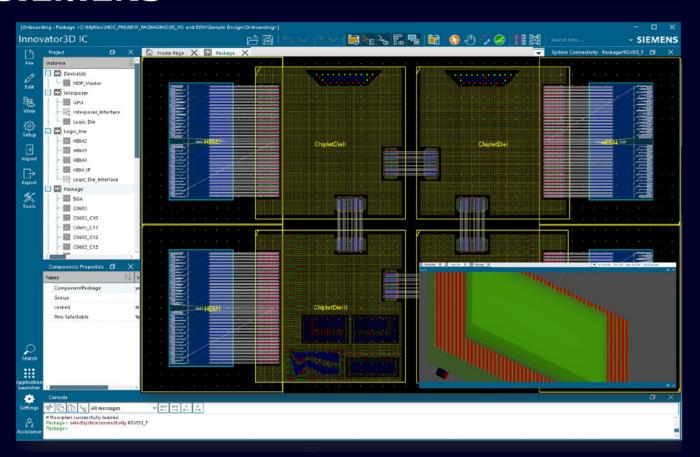

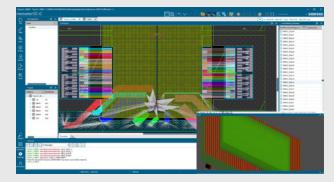

#### **SIEMENS**

## Facing semiconductor scaling challenges?

**Innovator3D IC** delivers the fastest and most predictable path for planning and heterogeneous integration of ASICs and chiplets using the latest semiconductor packaging 2.5D and 3D technology platforms and substrates

Your complete solution for 2.5/3D IC packaging design and verification

siemens.com/3DIC

#### CONTRIBUTING AUTHORS

Todd Burkholder, co-author of Taking 3D IC Heterogeneous Integration Mainstream, is Senior Writer and Editor at Siemens DISW, working with SMEs and customers to create content for the majority of EDA technology divisions at Mentor

Graphics and Siemens from 1997 on. He began his career in high-technology marketing in 1992 after earning a Bachelor of Science at Portland State University and a Master of Arts degree from the University of Arizona.

Jillian McNichol, author of How Arizona is Growing its Advanced Packaging Capabilities, is a technology blogger with more than seven years of experience covering a variety of topics in the microelectronics space. Jillian's

blog, Interconnectology 101 is featured regularly on 3D InCites. Her primary focus is technology trends such as Al and machine learning. She's also covered semiconductor manufacturing and advanced packaging processes. Jillian holds a bachelor's degree in journalism and mass communication from Arizona State University.

Peter Dijkstra, the author of 2024: A Year of Growth and Innovation, is Chief Commercial Officer at Trymax Semiconductor. He joined the team in 2021, coming from ASM Pacific Technology, where he served as director of sales, service, and

marketing from 2014-2021. Prior to ASM, Peter spent his career working with plasma-based technologies in the semiconductor equipment space, including ALSI, Nanoplas, Tegal, Alcatel, and the Plasma Physics Research lab.

Isabella Drolz, author of Bridging the Semiconductor Talent Gap - The Role of the European Chips Act and Beyond, serves as the Vice President of Marketing & Product Strategy at Comet AG's X-ray Systems Division. In her role, Isabella oversees Market

and Product Management, Global Application & Training Centers, Marketing, and the Academia Program. She holds a degree in industrial engineering, a Bachelor of Science in International Business Administration, and an MBA from Southern Nazarene University in Oklahoma City, USA. With a strong background in mechanical and plant engineering, Isabella has held several management roles focused on market-driven product and business development.

Dean W. Freeman, the author of Asia May Still Be the Hottest Spot for Advanced Packaging, is a technology advisor and a twicemonthly contributor to 3D InCites. He covers heterogeneous integration and sustainability topics as they

pertain to the greater semiconductor industry. Dean has over 40 years of life experience in the semiconductor manufacturing and materials space, where he has had experience in nearly every sector of the semiconductor manufacturing process. He has worked both in the fab and for semiconductor equipment manufacturing companies. Dean is also a Subject Matter Expert at Kiterocket, Prior to joining 3D InCites, Dean was a research VP for Gartner tracking semiconductor manufacturing, process technology, and multiple aspects of the internet of things. He has also worked at FSI, Watkins Johnson, Lam Research, and Texas Instruments. Dean has 9 process and equipment patents and has written multiple articles in various trade and technical journals. He holds a BS in Chemistry and Earth Science and an MS in Physical Chemistry.

Avery Gerber, author of US-JOINT Consortium: Strengthening Advanced Packaging Innovation Across Borders is a 3D InCites Community Intern. Currently pursuing a degree in International Studies and Journalism at Texas A&M University,

Avery brings a passion for written communication and a keen interest in the ever-evolving landscape of technology.

Julia Freer, author of What You Need to Know About PFAS, is an author and business owner on a mission to make manufacturing more environmentally responsible. She has a background in engineering, journalism, content writing,

and teaching and holds a Ph.D. in materials science. Julia's company, JLFG Communications, works with manufacturers to help them connect business goals, environmental action, and effective communication strategies. Julia's first book, Material Value, is a B.R.A.G Medallion Honoree, Finalist in the 2019 San Francisco Writers Contest, and Semifinalist for the 2020 Nonfiction BookLife Prize. She is also the author of Rethink the Bins, which received a Gold award from the Nonfiction Authors Association, Beyond the Green Team, and Materials & Sustainability.

Paul Lindner, author of Navigating the European Chip Renaissance is EV Group's executive technology director. He heads the R&D, product and project management, quality management, business development

and process technology departments. Lindner also leads customer orientation throughout all steps of product development, innovation and implementation in a production environment. He joined the company in 1988 as a mechanical design engineer and has since pioneered various semiconductor and MEMS processing systems, which have set industry standards. Prior to his appointment as executive technology director. Lindner established a product management department at EV Group. During that time, he was involved in marketing, sales, manufacturing, and on-site process support.

Tony Mastroianni, co-author of Taking 3D IC Heterogeneous Integration Mainstream, is the Advanced Packaging Solutions Director at Siemens Digital Industries Software. He has more than 30 years' experience as an engineer and

engineering manager in the global semiconductor industry and currently leads development of advanced packaging solutions for Siemens EDA. Prior to joining Siemens, he served in engineering leadership positions at Inphi and eSilicon. Tony earned a B.S.E.E from Lehigh University and a M.E.E at Rutgers University.

Camden McCrea, author of From Words to a World of Chips: Mv Experience with IMAPS and The International Symposium is an Honors International Studies student at Texas A&M University with additional studies in Business

Administration and Spanish. Writing, communication, and people are his passions and he hopes to combine all three to connect with and learn about people all around the globe.

Juliana Panchenko, coauthor of "The "White House of Microelectronics Packaging" Celebrates 15th Anniversary!", is a head of the group "Micro-/ Nano Interconnect" at Fraunhofer IZM-ASSID since 2014. She

holds a professorship at the Institute for Electronics Packaging Technology at TU Dresden. She has 14 years of experience in academia and research institutes and focuses on development and characterization of new interconnect technologies for fine-pitch applications of microelectronic packaging. She is an author of around 60 scientific publications.

Dr. Scott Sikorski, author of Empowering the Future: New York's Semiconductor Surge in 2024 is responsible for business development and offering management for the IBM Bromont OSAT facility as well as for driving

the IBM Research Heterogeneous Integration and Chiplet ecosystem development. He also guided development of IBM's Al hardware partner ecosystem. Dr. Sikorski started his career in 1989 with IBM Microelectronics holding positions in R&D, manufacturing, product line management, business development and complex deal negotiation over a 20-year period. He rejoined IBM in 2020 after a decade at STATS ChipPAC and JCET. Dr. Sikorski served on the Boards of Directors of industry organizations iNEMI and MEPTEC for several years. He received his Bachelor of Science degree from Columbia University's School of Engineering and Applied Sciences in Metallurgical Engineering and his master's degree and Ph.D. from the Massachusetts Institute of Technology, both in Materials Engineering.

Jim Straus, author of Cost-effective. High-performance Chips Are Driving the Move to Panel-level Processing, has served as ACM's Vice President of Sales for North America since April 2020. He has 30 years of experience in semiconductor equipment sales,

business development, account management, and operations supporting leading global semiconductor manufacturers. Jim holds a BS from the United States Military Academy, West Point, and an MBA from Fisher College of Business at The Ohio State University.

Ramachandran (Ram) Trichur, author of Face It: Live Events Strengthen Partnerships and Influence Product Innovation is the Global Market & Strategy Head for Semiconductor Packaging at Henkel Adhesive Technologies, Electronics.

With over 20 years of expertise in semiconductor industry in variety of roles with hands-on experience in wafer fabs and in heading business for specialty chemicals for electronics manufacturing, Ram oversees strategic and financial objectives for the market at Henkel. Ram holds an M.S. in Electrical Engineering from the University of Cincinnati and completed executive education in Business Management at Stanford Graduate School of Business. He holds 3 patents and has authored over 40 publications in leading conferences and industry journals.

Frank Windrich, Ph.D. coauthor of "The "White House of Microelectronics Packaging" Celebrates its 15th Anniversary!", is deputy head of Fraunhofer IZM-ASSID and leads the group "Lithography and Polymers for

Wafer-Level Packaging". He joined Fraunhofer IZM-ASSID in 2010 and realized multiple industry R&D projects in the field of advanced 3D wafer-level packaging, and wafer-scale integration technologies. He holds a degree in chemical engineering and doctoral degree in polymer chemistry.

3DInCites.com 3D InCites Yearhook

The next generation CA20. Made for the fab.

#### **Interconnectology Saves the World!**

By Françoise von Trapp

In 2007, when I was managing editor at the now defunct Advanced Packaging Magazine, we went out on a limb in our January Industry Forecast to declare, as our cover story: Advanced Packaging Saves the World! In 2008, we tempered that declaration

to Advanced Packaging Drives the Industry! By 2009, we were in the midst of a downturn, and the January cover story was titled Weathering the Storm. Halfway into January, the magazine folded.

Despite that, I never lost faith in the promise of advanced packaging. I staked my career on it by launching 3D InCites in July 2009. Were we clairvoyant? I'd like to think we were just paying attention. Fan-out wafer-level packaging and 3D integration technologies were in the early stages of development, and we followed them closely. While most of the semiconductor industry was still in hot pursuit of Moore's Law, EUV lithography, and 450mm wafers, we were focused on through-silicon via (TSV) fabrication and emerging developments in hybrid bonding.

Nonetheless, it was never really the packaging part that would save the world. It was the emerging advances in interconnect technology that caught the attention of the semiconductor industry as traditional CMOS scaling slowed. How do we improve power, performance, area, and cost? Chiplets are the answer and advanced interconnect processes that make them possible. Imec's Luc Van den hove calls it CMOS 2.0. We call it Interconnectology.

Now, as regions around the world race to be leaders in semiconductor manufacturing, they also recognize that advanced packaging and interconnectology are the keys to it all. The semiconductor industry and governments worldwide recognize this. Investments in advanced packaging innovation were the big stories in 2024 and will continue to be so in 2025. That's why we dedicated a special cover section to *Advanced Packaging Around the Globe* in this issue of the 3D InCites Yearbook.

Our newest technology blogger, Jillian McNichol, kicks things off with her article, "How Arizona is Growing its Advanced Packaging Capabilities". She paid visits to several of our members located in the Greater Phoenix area to learn how the state's investments are impacting them. In <u>US-JOINT Consortium: Strengthening Semiconductor Innovation Across Borders</u> 3D inCites intern, Avery Gerber interviews our community members participating in this collaboration organized by Resonac. Dean Freeman provides his market researcher perspective with <u>Advanced Packaging in Asia</u>. Spoiler

Alert: the region still reigns supreme for advanced packaging. I report back from visits to two member companies that are expanding operations in the Midwest and East Coast: NHanced Semiconductors in Odon, Indiana, and Raleigh, North Carolina; and Onto Innovation with its PACE Center in Massachusetts.

This special section also features contributed articles by members of the 3D InCites community. IBM's Dr. Scott Sikorski provides an update on advanced packaging in the Northeast Corridor. EV Group's Paul Lindner helps us navigate the European chip renaissance. Frank Windrich and Juliana Panchenko celebrate Fraunhofer IZM-ASSID's 15th anniversary with the article, Fraunhofer: The White House of Advanced Packaging.

The issue also features contributions on other topics that were top-of-mind for 2024. You'll get an update on the PFAS situation from Julia Freer. Jim Straus, of ACM Research writes about what's driving the move to panel-level packaging. Tony Mastroianni and Todd Burkholder, Siemens EDA bring you the latest update on taking 3D IC heterogeneous integration mainstream.

Isabella Drolz, Comet Yxlon writes about closing the gap on the European talent shortage. Henkels' Ram Trichur describes the benefits of attending industry events, and Texas A&M senior, Camden McCrea, shares his experience as an intern with IMAPS and attending the IMAPS Symposium.

Simon McElrea, who, along with Scott Jeweler, helped coin the words interconnectology and interconnectologist, once told me that to him, interconnectology means more than a toolbox of interconnect solutions – it means intercompany collaboration.

We couldn't agree more. That's why 3D InCites is more than just a platform. It's a community of interconnectologists. So we've launched some networking events adjacent to major conferences to foster that community feel. In March, in addition to our annual 3D InCites Awards ceremony, we held the first BackYard Olympics in collaboration with the IMAPS Device Packaging Conference. In November, the day before SEMICON Europa, we celebrated all things interconnectology at the 3D InCites Member Stammtisch and the inaugural Interconnectology Eisstockschiessen Invitational hosted by LQDX. Check out the <u>Year in Pictures</u> to see how much fun we had making connections at all these events. We're already looking forward to continuing these traditions in 2025.

So in more ways than one, this issue celebrates all things interconnectology. Will it save the world? Who knows. But one thing is for sure, we're going to have fun trying.

Junguise

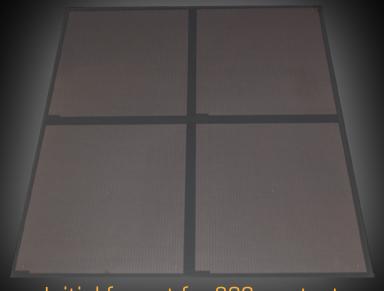

thinkdeca.com

Realizing the full value of **sem**<sup>1</sup> standard 600mm square panels

#### Initial format for 300mm test

designed to utilize existing industry 300 mm probe capacity

Current optimized format

full 600mm active area for maximum utilization

#### Cost-effective, High-performance Chips Are Driving the Move to Panel-level Processing

By Jim Straus, ACM Research

Artificial intelligence (AI) is driving the need for faster processing speeds to keep up with the large language models. As a result, we see multi-reticle packages using 2 x 800 mm² chips in production in a single package. These larger chip sizes and the need for better yields and higher capacity drive the move from wafers to larger rectangular substrates for the packaging process. The move to fan out panel-level packaging (FOPLP) is partly driven by the industry's move to packaging chips on a substrate to reduce the limitations and constraints of the wafer-level packaging process. The rapid adoption of multiple-reticle chiplets has created packaging shortages as the FOWLP packaging process is capacity-constrained due to the large size of these packages.

To improve the capacity situation, packaging companies are working to develop panel-level packaging (PLP). Instead of using a round wafer in the packaging process, a square substrate will be used for PLP. AMC Research (AMCR) has a long history of success with wafer-level packaging (WLP), and it is supporting the transition to PLP with new approaches for cleaning and deposition technologies. Before we move into some details of PLP, however, let's discuss why we need to move to larger substrates in the first place.

#### Large-package Design Challenges

Building packages that are larger than 2 x 800mm² has multiple challenges. One of the biggest issues is how many 800mm² chips can be placed on a 300 mm wafer or packaging substrate. With a chip size of ~800mm², about 64 chips can fit on a round 300mm wafer. However, this does not consider yield. The chip is square and the wafer is round, so a significant amount of substrate goes to waste in the chip's processing. This is because a considerable amount of area at the edge is lost due to the mismatch in shape.

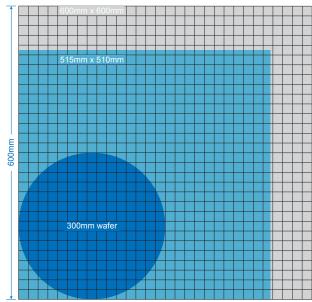

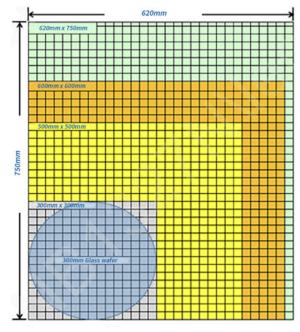

To help resolve packaging supply chain constraints, the packaging industry is moving from round substrates to square panels. Both wafer manufacturers and outsourced assembly and test (OSAT) packaging suppliers have proposed using square glass panels as the substrate for packaging the large-area chiplets. This will significantly increase the number of chips that can be processed on a single panel and should ease current supply constraints. The industry for now has settled on panel sizes of 515mm x 510mm, which has 3x the area of a 300mm silicon wafer; and 600mm x 600mm, which has 5x the area of a 300mm wafer (Figure 1).

Figure 1: 300mm wafer compared to 515mm x 510mm and 600mm² panels

#### **Advantages of Panel-level Packaging**

Transitioning to PLP has some advantages over WLP. For example, PLP enables the industry to significantly increase the substrate area for building chiplets, improving yield and lowering packaging costs. The larger area allows more chips to be assembled simultaneously, increasing capacity and thus reducing the current supply constraints. FOPLP will allow for the integration of various die technologies (e.g., logic, memory, and RF) more easily in a single package, which supports more complex system designs.

Continued on page 69

#### What You Need to Know About PFAS

#### By Julia Freer, JLFG Communications

You have probably heard about health and environmental concerns related to per- or polyfluoroalkyl substances (PFAS). Companies are being pressured to replace PFAS with safer alternatives for nonstick coatings, waterresistant fabrics, firefighting foams, and more to meet upcoming restrictions. For manufacturers, including those in the semiconductor industry, PFAS replacement is incredibly complicated.

#### **The Proliferation of PFAS**

PFAS are used in nearly every step of the semiconductor manufacturing process, from lithography through packaging. This isn't merely a concern for companies making and purchasing process chemicals. The consequences of PFAS use apply to every company in the industry, whether a facility makes chemicals, materials, equipment, or components. Even companies that outsource all their manufacturing probably have PFAS in their buildings, and they should also know what their vendors are doing.

Some applications of PFAS are common to multiple manufacturing sectors. Items such as tubing, fittings, cables, filters, valves, pumps, lubricants, and power supplies are relatively universal. The semiconductor industry can learn from what other sectors are doing to replace PFAS and join forces to advocate for PFAS-free supplies and components. However, what works for, say, industrial or automotive sectors might not be high enough purity to be compatible with semiconductor particle contamination limits.

Other PFAS uses are industry-specific. Fluorocarbon gases are required to etch silicon. Photoacid generators (PAGs) and etchants containing PFAS enable 193mm and UV lithography. The list goes on. Research into PFAS-free alternatives is ongoing, but we are still many years away from workable substitutions that meet yield, performance, and productivity requirements.

Companies should continue R&D efforts to replace PFAS and invest enough to accelerate progress. Meanwhile, there are several urgent issues that our industry needs to consider related to newly enacted and upcoming legislation about PFAS.

#### **The Regulatory Environment**

As legislation restricting the use of PFAS proliferates, action is becoming a matter of compliance. While most of the proposed laws banning PFAS target consumer goods, there are several issues for our industry to consider: reporting requirements, wastewater treatment, and supply chain risk. But first, let's talk a bit about existing and pending legislation.

The widespread PFAS ban that the European Chemical Agency (ECHA) proposed in early 2023 is still under discussion. SEMI and the European Semiconductor

Industry Association (ESIA) were among many industry groups that submitted feedback. They requested a 12year derogation for the entire semiconductor industry supply chain. This is based on the critical role that our industry plays in multiple end markets and the difficulty in replacing PFAS in our manufacturing processes.

The regulatory situation in the U.S. is complicated by a multitude of laws that are in effect or under consideration in over half the states. A search of legislation with the keyword "PFAS" results in over 500 entries for federal and state measures. I attempted to review legislation intending to restrict PFAS use and quickly became overwhelmed.

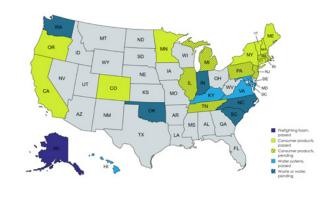

The map in Figure 1 color-codes states according to the most extensive bill passed or under review. Some states that intend to restrict PFAS in many categories of consumer products, for example, also have laws relating to wastewater management, firefighting foam, or PFAS monitoring. (Caveat: I don't guarantee that the map is 100% correct, but it gives an idea of the scope of PFAS legislation.)

Figure 1: U.S. Map Highlighting states with passed or pending legislation regulating PFAS use

A recently passed law in Minnesota is the most farreaching to date. It bans PFAS in eleven categories of consumer products beginning January 1, 2025, and in "any product that contains intentionally added PFAS" in 2032, with an exception for "currently unavoidable use." Laws in several states, including California, Oregon, and New York, restrict PFAS in one or more consumer product categories as of January 2025. Other similar state restrictions will take effect in 2026. Pending laws in several states mimic the wording of the Minnesota bill.

Most state-level bills aim to eventually phase out all "unavoidable" PFAS use, though they don't clarify how they determine whether a use is unavoidable. The bills start with bans on intentionally added PFAS in specific consumer goods categories, as noted above, with provisions five to eight years out that extend to

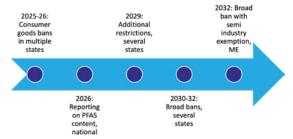

unintentionally added PFAS and to any product where substitution looks possible. The broadest restrictions will take effect between 2030 and 2032. Figure 2 presents a general timeline.

As of October 2024, Maine's bill is the only one to specifically list semiconductors as a product category exempted from the 2032 PFAS phase-out. Other states will likely follow suit before the broadest restrictions come due.

Figure 2: Timeline of passed and pending PFAS regulations

#### Reporting

For companies outside the consumer goods industry, the immediate need is to plan for reporting requirements from the U.S. Environmental Protection Agency (EPA) that will take effect in January 2026. Some states have separate reporting laws, but federal law may override those. According to the EPA requirements, companies will need to report on their PFAS usage dating back to 2011. Any entity that manufactures PFAS chemicals or PFAS-containing products is obligated to collect and share a multitude of data, including:

- The quantities of each specific PFAS used and how it is used in the manufacturing process

- Description of byproducts resulting from manufacturing, processing, or disposal

- Environmental and health effects of all PFAScontaining substances or mixtures

- Plans for disposal of all of the above

If you don't have a plan for generating and tracking the data, it's time to start. Data collection will require tracking suppliers of all chemicals and components to discover whether those items contain PFAS. The EPA's 138-page reporting instructions document contains all the details.

#### **Wastewater**

From a public health perspective, keeping PFAS and other toxic chemicals out of our soil, water, and air is critical. PFAS laws relating to water systems or waste treatment are also relevant to our industry because they apply to any facilities in the state regardless of what they make or what industries they serve. Discharge of PFAScontaining waste, whether accidental or not, can carry fines or get a company sued.

A New Hampshire bill, which the governor signed in August 2024, exposes any PFAS facility releasing hazardous waste containing PFAS into ground or surface water to liability. The concentration that triggers the

regulation is 10 parts per billion (ppb). The bill, which also restricts PFAS in consumer goods, defines a PFAS facility as "any site, area, or location where PFAS is or has been used in a manufacturing process."

The best way for a fab or other manufacturing facility to ensure they don't run afoul of water-related PFAS regulations is not to release these chemicals into the environment. A combination of on-site filtering and recycling can accomplish this goal. Something as simple as installing activated charcoal water filters or reverse osmosis systems can stop PFAS from entering the public water system. Water testing will verify if your filtration is sufficient.

#### **Supply Chain Risk**

Even legislation that does not directly restrict the use of PFAS in semiconductor manufacturing can affect our industry if we cannot procure these chemicals. In late 2022, 3M announced its intention to exit PFAS manufacturing by 2025, and the company intends to follow through. Given 3M's history of supplying PFOA and its \$10-12 billion settlement to support remediation of PFAS in US public water supplies, the move makes sense for the company even without the demands of the Minnesota law prohibiting PFAS manufacturing.

The question is how 3M's move will affect the supply chain. Its customers will be forced to switch suppliers. perhaps outsourcing to countries without strict environmental regulations regarding disposal and wastewater treatment.

Regulations restricting PFAS use in consumer goods may also affect the cost and availability of these chemicals in our industry. Suppliers threatened with lawsuits may decide to exit the market or indirectly pass the cost of legal bills to their customers. As a minor player in the global PFAS market, semiconductor companies have limited clout. For example, the semiconductor industry buys a tiny percentage of global production of several fluoropolymers that are used extensively to make all sorts of equipment. It may be especially hard to secure shipments of these materials.

#### Do Something

It's a good idea to understand your company's risk regarding PFAS. Do you know what PFAS are in your facilities? Have you contacted suppliers to learn about potential supply chain disruptions due to pending PFAS regulations? Do you know what's in your wastewater?

If you want to stay abreast of the ever-changing regulatory landscape and have a say in our industry's response to PFAS risk, you can participate in one of SEMI's PFAS working groups or the Semiconductor Industry Association's PFAS Consortium. Dozens of companies in our industry are involved in discussions around supply chain resiliency, transparent communication, and transition strategy. The long-term goal is to finalize an industry roadmap for PFAS detection, replacement, and remediation, along with standardized communication to ease the burden of meeting reporting requirements.

3DInCites.com 3D InCites Yearhook 11

Revolutionizing the World of Advanced Packaging

Amkor's S-SWIFT™ technology is a game-changer in heterogeneous IC packaging. It enables high-performance, cost-effective integration of multiple chiplets and memories.

This technology increases I/O and circuit density, paving the way for advanced 3D package structures, making it indispensable for next-gen mobile and networking applications.

Follow us @amkortechnology © 2024 Amkor Technology, Inc. All Rights Reserved.

## Taking 3D IC Heterogeneous Integration Mainstream

By Tony Mastroianni and Todd Burkholder, Siemens EDA

Over the last several years, chiplet-based heterogeneous package integration has emerged as a promising alternative to traditional monolithic package solutions; the so-called homogenous SoC design. 3D IC heterogeneous integration is a system approach, wherein what typically would be implemented as an SoC is disaggregated into solid, fabricated IP blocks; i.e., chiplets.

These chiplets typically provide a specific function implemented in an optimal chip process node. Several chiplets and an optional, custom SoC device can be mounted and interconnected in a single package using high-speed/bandwidth chiplet-to-chiplet interfaces. The resulting 3D IC heterogeneously integrated packages deliver greater performance at a reduced cost, higher yield, and have only a slightly larger area than a traditional monolithic SoC package.

This system-oriented approach, known as system technology co-optimization (STCO), differs from traditional IC design. STCO spans five significant activities that are both complex and sophisticated: architectural planning and analysis, functional design and test, physical design planning and verification, and electrical and reliability analysis.

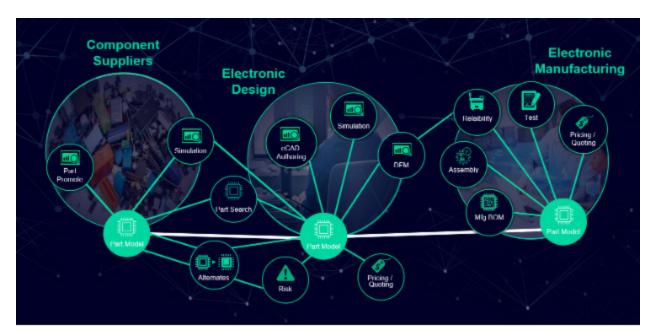

Exchange (CDX) was established within the Open Compute Project (OCP) to promote and support this technology and eventually deliver it to the mainstream. The CDX group comprises EDA vendors, Fabs, OSATs, and substrate material providers. The charter of the CDX group is to promote a chiplet ecosystem by defining models that are necessary to support the 3D IC design process, as well as the different types of design kits that this requires. Therefore, we set out to establish an ecosystem of design kits to enable 3D IC design throughout the semiconductor industry and address the fact that the packaging community has lacked the well-structured design kits and PDKs available for traditional ASIC technologies.

The idea was that we could eventually have reusable chiplets out in the marketplace, and that's what we're promoting in the CDX group. Therefore, it was critical to develop and leverage existing standards for the various 3D IC design kit formats (which we call 3DKs), and we wanted the 3DKs to be in machine-readable formats that can be consumed by the tools and the workflows. In turn, we needed to have the EDA companies support these workflows and the different formats. Finally, to make the critical link to manufacturing, the OSATs—the

foundries that generate the data for these different design kits—also had to be part of this ecosystem.

## Architectural Planning & Analysis Functional Design & Test Physical Design Planning & Planning &

Figure 1: 3D IC heterogeneous integration requires a co-design and co-optimization approach (STCO).

With this new approach come many advantages, opening new possibilities in electronic system design; however, the question facing us is how to facilitate the adoption of this exciting yet esoteric 3D IC methodology, one requiring a high degree of expertise and effort.

With that guest in mind, in 2021, the Chiplet Design

#### The 3DKs: 3D IC Design Enablement

As mentioned, the IC design process has a very structured, well-defined design enablement infrastructure. It includes IP: the reusable building blocks of SoC designs. There are process design kits, which include the technology rules for creating extraction decks, place and route decks, et cetera. There are

also macros for memory and analog signal-type designs. We're trying to extend that concept for many things in the packaging world, but a different set of design kits is required. So, 3D IC design requires a comprehensive set of new design enablement kits to support the design, verification, and handoff to manufacturing.

These design enablement kits fall into five key areas, as reflected above. These are physical design, electrical

analysis, reliability analysis, and test that start up front during planning. Also, as parts are delivered for manufacturing, test factors both for the individual chiplets as well as the complete system-in-package (SiP) must be generated.

To support the needs in all these key areas, we are developing four 3DKs to provide a comprehensive set of design enablement kits that support the design, verification, analysis and testing of 3D IC designs.

- Chiplet Design Kits (CDK): Recommended chiplet models to support the integration into a 3D IC design

- Package Assembly Design Kits (PADK): Chiplet IO/TSV pitch spacing rules, substate/interposer width/ spacing, routing rules, and general-purpose package component placement rules

- Material Design Kits (MDK): Composite material properties for package components to support electrical and reliability analysis

- Package Test Design Kits (PTDK): Defines test IO pins, dimensions, and function to support ATE test hardware and testing

#### **Chiplet Design Kits**

CDK models are created or reused for early architectural, test, and physical design planning. These are the models that are required to design a chiplet. So, the first thing the CDX group did was determine the design models required to integrate a chiplet into a package. Our first effort involved working with the JEDEC group.

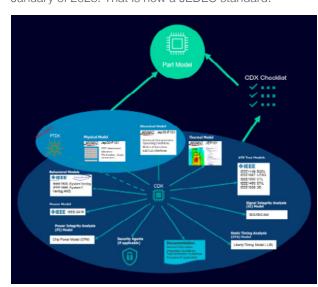

The JEP30 PartModel was designed to describe electronic components used in a PCB design. As we were trying to do a similar thing for 3D ICs, we asked them to help us extend that part model to support chiplets. Together we came up with a list of chiplet design models that we recommend be included with a chiplet. The idea is that we could eventually have reusable chiplets out in the marketplace. And we drove that extension to the JEP30, the PartModel, back in January of 2023. That is now a JEDEC standard.

Figure 2: Chiplet design kit (CDK): JEDEC JEP30 PartModel.

We next developed checklists for other formats and recommended the models required to support design analysis. At a minimum, we have a checklist to know what models are available. A chiplet designer or chiplet provider can define which models are available. There are also provisions where we can include the models, and that's really up to the chiplet provider if they want to include that in the part model.

#### Package Assembly Design Kits

Today, we are actively working on the package assembly design kits. These include the rules for defining pitch, spacing, and the type of connectivity components used to connect the chiplets to the interposers and substrate.

In keeping with our guidelines, they are in a machine-readable format, and they are EDA-neutral. Thus, each of the EDA vendors, assuming they're supporting these formats, would be able to take those rules from a single source. This results in much cleaner access for the FABs and the OSATs during manufacturing, because they can provide these rules in one format that all the EDA tool vendors can use. With access to this information and these machine models, the PADKs can be used for scripting directly in some of the EDA tools.

#### **Material Design Kits**

Another area we are working on is material design kits. These are a truly novel idea. When engineers are doing analysis—whether it be thermal, stress, signal integrity, or power integrity—the MDKs can define the material properties that are in the package components inside the package. Again, the idea is to put these in a machine-readable format, rather than having that information derived ad-hoc from the vendors and material providers and manually input into the tools. Then the tools would use the MDKs to use that material information directly for analysis.

#### Package Test Design Kits

As the name implies, package test design kits are for test. The chiplet model contains a lot of information in terms of the physical dimensions of the device, also the pins, and the functional mode. But when you're testing these devices, typically there is a different set of pins that are used to test for wafer sort when you're testing the wafers. The PTDKs define the location of those pins, the modes, the physical location, the shapes, and all the geometries.

#### **Workflows to Support 3D IC**

Another benefit of a PartModel, and one of its targeted purposes, is to enable a chiplet market ecosystem. Chiplet suppliers can design a chiplet, and if they want to offer that to the market, they can describe all the required information and make it available.

This gives chiplet suppliers the ability to define essentially the information about their products in an electronic catalog, in which designers can see the different available parts and choose the ones best suited for their particular design.

Figure 3: Bridging the chasm in the electronics value chain.

Thus, chiplet providers can empower prospective customers to search for their chiplet IP and assess functionality, detailed electrical/physical attributes, and available design models. System designers and chiplet consumers can then look through that catalog and also do business transactions. Finally, the 3DK models can be used for the design and verification process, and eventually handed off to manufacturing.

Lastly, we are advancing the development of the authoring tools required to create these models. The 3DK models are in CDX format, and this is not a friendly

format for someone to type, so there is a need for an open-source EDA-neutral authoring tool. The goal is to have a single tool that will create each of these 3DK models, and the specific EDA vendors, manufacturers, and assemblers would then use the EDA-specific implementations to create the decks, etc. Toward that end, Siemens EDA introduced Innovator3D IC. Innovator3D IC offers a comprehensive multi-physics cockpit for 3D IC design, verification, and manufacturing to deliver a fast, predictable path for the planning and heterogeneous integration of ASICs and chiplets.

Figure 4: The Innovator3D IC - heterogeneous integration cockpit.

As this article has attempted to show, the CDX working group has been hard at work to provide the open source, EDA neutral, machine-readable 3DKs and chiplet

authoring tools that will propel 3D IC heterogeneous integration into the mainstream of electronic systems design. And we'll be coming to your town very soon.

3D InCites yearbook

# Spots Advanced Packaging Around the Globe For those of you who recognize the double entendre in the title and question the focus of this year's cover feature, let me assure you: It's not about thermal management

solutions for next-generation advanced packaging. It is about the rising importance of advanced packaging and the activities that it's stimulating around the globe.

For decades, semiconductor packaging was nothing more than a necessary step to ensure the connection and protection of semiconductor chips on the circuit board and nothing more. Because it was a cost adder, the industry goal was to do it as cheaply as possible. Most semiconductor manufacturers in the U.S., Asia, and Europe shipped their packaging offshore.

As Moore's Law slows, heterogeneous integration approaches using advanced packaging technologies are now critical to ensuring the power, performance, area, and cost requirements for today's leading-edge processors. This fact is changing the global importance of advanced packaging, which has become a value-add to system-level performance.

Five years ago, when the COVID pandemic created a global chip shortage, governments worldwide recognized how critical semiconductors are to our everyday lives. Simultaneously, geopolitical tensions increased and artificial intelligence applications demanded advanced Al chipsets.

This increased concern about the impact semiconductors have on national security. As a result, we saw increased investments from Europe, Asia, and the U.S. to build regional ecosystems for onshoring semiconductor manufacturing.

Many say that 2024 will go down in history as the Year of Advanced Packaging. As regions around the world compete for semiconductor manufacturing market share, they are all investing in advanced packaging R&D. Centers of excellence are popping up everywhere.

This issue of the 3D InCites Yearbook takes a deep dive into global advanced packaging activities in Europe, Asia, and North America, with a special focus on activities in Arizona. Read on!

## How Arizona is Growing its Advanced Packaging Capabilities

An inside look at how ASU, local governments, and private sector companies are working together to make Arizona a hub for advanced packaging innovation.

#### By Jillian McNichol

The year 2022 was monumental for the semiconductor industry. That year, the Biden-Harris administration committed to making the U.S. a world leader in semiconductor manufacturing by passing the bipartisan CHIPS and Science Act. In an effort to decrease the nation's reliance on China for chips, and to meet the demands of advanced technologies, the CHIPS Act highlighted plans to invest \$53 billion in onshoring semiconductor manufacturing, with \$1.6 billion going toward advanced packaging. (Figure 1)

Figure 1: YES is just one advanced packaging company investing in Arizona. Vic Chaudhry, VP and head of stragic marketing hosted Jillian McNichol at the YES facility in Chandler, AZ.

Due to current onshoring efforts for semiconductor manufacturing, it wouldn't make sense to build front-end capacity in the U.S. only to send the chips overseas to be packaged. With a major boost in funding pouring into the country's advanced packaging ecosystem, it's almost hard to believe that packaging was once regarded as little more than a cost burden. In a swift change of events, it's emerging as the industry's best chance for continuing Moore's Law. This famous industry observation states that transistors on an integrated circuit (IC) will double every two years.

To keep up with power, performance, area, and cost requirements, the industry is turning to advanced packaging technologies like 2.5D and 3D stacking. By optimizing the package, chip manufacturers can continue to pack more compute power in less space. This is essential for advancing artificial intelligence (AI), high-performance computing (HPC), and more.

As advanced packaging moves into the spotlight, Arizona is becoming a key player in this integral manufacturing process. As a result, local governments and private

sector companies are collaborating to boost Arizona's semiconductor manufacturing dominance.

#### **Arizona's Private Sector Growth**

In February 2024, Amkor announced the approval of its outsourced semiconductor assembly and test (OSAT) facility in Peoria, Arizona. Once the facility is completed, it will make history as the largest OSAT facility of its kind in the U.S. (Figure 2)

Figure 2: Rendering of the future Amkor Technologies Facility in Peoria, AZ

Amkor's \$2 billion investment will not only provide Arizona with a world-class packaging center, but it will also create 2,000 new jobs for Arizonans. In addition, Amkor is the only U.S. headquartered OSAT provider that offers both high-volume manufacturing and advanced packaging capabilities. Although the facility's opening date has yet to be announced, its creation marks a leap forward in strengthening Arizona's advanced packaging foothold.

Alongside its new facility, Amkor also announced a memorandum of understanding with TSMC to work together on delivering high-volume advanced packaging and testing technologies to its customers. The proximity of Amkor's upcoming back-end facility and TSMC's frontend fab will help further improve product cycle times, boosting industry activity in the Valley.

While I was interviewing companies for this article, I asked all of them why they chose to have a presence in Arizona. I received several answers, but access to government funding, proximity to local and California-based customers, and a robust talent pipeline came out on top. However, something I found particularly interesting was learning just how purposeful Arizona's move into advanced packaging has been.

"You have everybody from the governor down focused on growing a semiconductor ecosystem," said Eelco Bergman, Chief Business Officer at Sara's Micro Devices. Sara's Micro Devices opened its first Arizona manufacturing center in Chandler in January 2024. (Figure 3)

Figure 3: Eelco Bergman, Chief Business Officer at Sara's Micro Devices, hosted a visit with Jillian McNichol.

Bergman shared that Arizona's governmental organizations, such as the Arizona Commerce Authority (ACA), the Greater Phoenix Economic Council (GPEC), and city governments, are focused on attracting semiconductor companies. This strong government support, as well as competition between cities, helps bring the talent needed to create a thriving ecosystem.

"None of these companies, including ourselves, operate on their own," Bergman said.

Similar to Sara's Micro Devices, Yield Engineering Systems (YES) also opened a new facility in Chandler in July of 2023. Incidentally, the two companies share the building. (Figure 4)

Figure 4: YES and Saras share their home in Chandler, AZ.

Vik Chaudhry, VP and Head of Strategic Marketing at YES, mentioned that the company opened its new facility in Chandler to be close to two of its biggest customers - Intel and TSMC. The city's large talent pool and business-friendly climate also drew YES in.

The company has a strong focus on glass core substrates, and with the continued growth in this area of packaging, the company expects to add around 100 new roles in the foreseeable future.

#### Arizona State University's Role in the State's Semiconductor Ecosystem

With so much emerging innovation in Arizona, the state needs to build and retain a robust and talented workforce. Although workforce development has historically been a hurdle for the semiconductor industry, Arizona State University (ASU) is helping to bridge this gap.

"We have a close relationship with not just the city and the state, but also with ASU," said Ron Huemoeller, CEO of Sara's Micro Devices. "ASU has a significant amount of funding and effort going into package development that we are now a part of with them. There's a big assist with development and talent, and they also help us with access to the government."

But ASU isn't the only university in the U.S. that has semiconductor initiatives. Earlier this year, Northern Arizona University received a \$13 million grant from the ACA to fund its semiconductor metrology program. The University of Arizona also has a Center for Semiconductor Manufacturing, where students can earn a graduate certificate in microelectronics packaging. Additionally, the Maricopa County Community College District introduced a 10-day training program for semiconductor technicians.

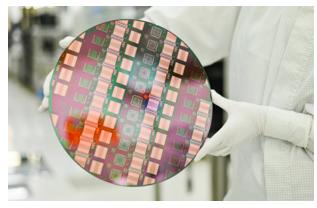

So I had to ask—what sets ASU apart from other schools across the country? From what I gathered, other schools also have stellar research capabilities, but they're not located in states where growing the advanced packaging industry at large is a top priority. To learn more about ASU's role in expanding advanced packaging, I visited ASU's MacroTechnology Works center in Chandler. While I was there, I spoke with key leaders from both ASU and Deca Technologies.

In March of 2024, the two organizations announced their partnership to create North America's first Fan-Out Wafer-Level Packaging (FOWLP) research and development capability. FOWLP is a packaging approach that helps build higher-density packages by fanning out the interconnects through a redistribution layer (RDL), and it does this at a lower cost than silicon interposer technology. FOWLP is important because high-density packages are becoming increasingly relevant for scaling AI, electric vehicles, and more.

#### The Relationship Between ASU, Deca, and the State of Arizona

Although the R&D center is still in progress, the partnership between ASU and Deca is very much alive. For instance, this past November, the National Institute of Standards and Technology (NIST) announced that ASU and Deca were selected to lead the SHIELD USA initiative. This project aims to promote innovation within the domestic advanced packaging industry, expand capacity, and help the U.S. regain its leadership in this area of microelectronics.

With so much in the works, I asked Zachary Holman, Vice Dean for Research and Innovation for ASU's Ira A. Fulton Schools of Engineering, about how the ASU and Deca partnership came to be.

In short, Holman shared that federal and state funding allowed ASU and Deca to form their partnership. Deca is a leading provider of advanced packaging technologies headquartered in Arizona, and the company is most known for high-volume FOWLP solutions that power many of the world's smartphones. In addition, ASU's Fulton Schools of Engineering had 33,000 students as of 2024.

However, ASU wasn't always strong in packaging, so I had to ask. What made ASU want to compete in this industry? Was this driven by the state's increasing need for packaging talent? The short answer is yes.

Holman highlighted that in 2020, ASU began working on its strategy for microelectronics in terms of university research, partnership, and innovation. He mentioned that ASU initially focused on materials due to its existing expertise in that area. The university soon expanded into advanced packaging to meet the needs of the local semiconductor ecosystem.

"We realized that we needed to produce the talent for these companies to hire and that we needed to have innovative faculty members who were teaching that next generation," Holman said. "So, we made a strategic play in packaging."

Holman also shared that Deca was a natural partner due to its proximity to ASU, and he emphasized Deca's advanced technology and natural understanding of ASU's goals. It was easy to find common ground, he said, because the company had a strong grasp on the future of advanced packaging.

Together, the organizations work to attract talent and align their efforts to meet the demands of Arizona's advanced packaging needs. Tim Olson, CEO of Deca, echoed the benefits of this partnership.

"We needed a partnership where we could have a physical facility and continue to innovate - to take what we had and continue to build future generations," said Olson. "ASU is perfect for that. Perfect location-wise, perfect mindset-wise."

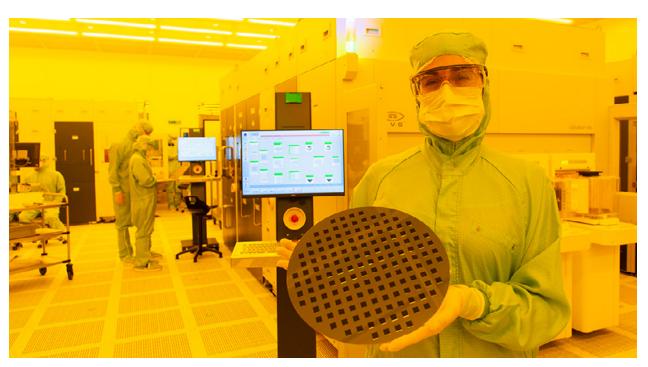

A big part of teaching the next generation of packaging professionals is providing them with hands-on experience. While I was at MacroTechnology Works, I asked Holman to explain the difference between gaining real-world experience at ASU and gaining experience as an intern in a fab (Figure 5).

Figure 5: The lobby at ASU's MacroTechnology Works. The cleanroom space is shared by ASU. Deca. EV Group, and Applied Materials.

"As an intern, you don't get to go into the fab and turn a knob, because you might break something," he said. "Internships are fantastic for students, but someone that is on a three-month summer internship isn't going to have responsibility."

With students gaining direct, hands-on experience with advanced packaging tools, Holman also shared advice for companies that want to engage students earlier on.

Students, he said, are using equipment that was donated by local companies, and those companies have engineers who come to ASU and explain how the tools are used in fabs. This approach helps turn students into ambassadors for the tool companies because they've worked on their systems before. Students may also end up working at the tool companies themselves.

#### Perspective From Long-Established Arizona Semiconductor Companies

As The CHIPS Act and local government funds made its way into the state, I wanted to know how recent growth impacted semiconductor companies that were already in Arizona. Did they benefit from any of this, or were they too far ahead of their time?

To find out, I revisited the MacroTechnology Works facility to meet with EV Group—a company that has been in Arizona since 1994. EV Group is headquartered in Austria and has a broad global presence, but its Chandler facility is home to a class 100 cleanroom and onsite equipment lab (Figure 6). While I was there, I spoke with Vineeth Reddy Bijjam, the company's Director of Technology and IP.

Figure 6: A peek inside EV Group's Class 100 clean room located in MacroTechnology Works.

Right from the beginning, EV Group's founders believed that Arizona would become an epicenter for semiconductor technology. Although the company didn't receive state or federal funding, Bijjam shared that EV Group benefits from local growth indirectly because its customers are now incentivized to come to the state.

"Our lab is a strategic piece of infrastructure that's helping us partner with local customers," said Bijjam. "We engage with them in the very early stages of development and provide them with a shorter feedback loop, so they don't have to wait for broader lead times to get their prototypes."

**8** 3DInCites.com

In addition to customer partnerships, Bijjam also highlighted EV Group's active internship program with ASU and the company's relationship with several university professors.

Finetech is another global company with a longstanding Arizona location. Opened in 1999, Finetech's Mesa, Arizona location is home to its sales and support center for all equipment it sells in the U.S. The Mesa location also features a showcase room with all of the company's equipment, so customers can run feasibility trials and access Finetech's process development services. (Figure 7)

Figure 7: EV Group's Vineeth Reddy Bijjam, Director of Technology and IP, hosted Jillian McNichol's visit.

"University sales have really picked up in the past year, specifically due to funding from the CHIPS Act," said Neil O'Brien, General Manager at Finetech Americas.

O'Brien also highlighted increasing opportunities for Finetech to work with customers on process development and experimentation initiatives, specifically on projects that have received funding from the CHIPS Act.

#### **Key Takeaways**

Arizona is working to create a robust advanced packaging ecosystem, with all parties working effectively together to build the future of this industry. Local governments are incentivizing businesses to bring their advanced packaging capabilities to Arizona, and ASU is working to educate and train the next generation of packaging professionals in accordance with the needs of Arizona's local companies.

Although companies that had a pre-existing presence in Arizona aren't benefiting from funding directly, the influx of new businesses in the state has led to increased tool sales, partnership opportunities, and access to a broader talent pool.

Will Arizona be able to maintain its momentum and establish itself as a North American hub for packaging innovation? Only time will tell, but I'm optimistic for the future.

#### **2024: A Year of Growth and Innovation**

#### By Peter Dijkstra

2024 was another year of significant growth for Trymax Semiconductor Equipment B.V. This year was marked by several pivotal developments, including the successful ramp-up of our new manufacturing facility, the establishment of a dedicated quality department, the expansion of our team with additional Field Service Engineers, and the growing momentum of our USA team, which resulted in multiple purchase orders.

In the broader market, while the automotive sector remains stable, particularly in silicon carbide (SiC) applications, other markets have experienced slower growth. However, we have observed a substantial increase in the storage and availability of data, with ambitious forecasts driven by the increasing demand for high-speed data access everywhere.

The most substantial growth for Trymax this year came from advanced packaging applications. Our process team has been dedicated to developing various process applications related to 2D, 2.5D, and 3D packaging technologies. In 2D IC packaging, components are arranged on a single plane. In 2.5D IC packaging, components remain on the same plane,

but an interposer allows for additional integration. 3D IC packaging involves vertically stacking components, enabling higher levels of integration and potentially improved performance and power efficiency. These devices are increasingly interconnected using through-silicon vias, which are fabricated using the Bosch process.

Our Trymax Process Module excels at efficiently cleaning residual polymer after the Bosch process. Additionally, to facilitate easier copper filling of the created vias, our Process Module is capable of creating a bowl etch on top of the vias.

Before Chip-to-Wafer (C2W) or Wafer-to-Wafer (W2W) stacking, it is essential to clean and, where possible, activate surfaces. Our Trymax low-cost Process Module simplifies this cleaning process while simultaneously activating the surface to make it more hydrophilic.

On behalf of the entire Trymax team, I would like to extend our heartfelt thanks to our customers and suppliers for the trust and confidence they have placed in us throughout this year.

The STILE™ offers a new paradigm for inpackage power delivery that significantly improves efficiency and performance while freeing up package real estate to enable higher levels of chiplet integration. A multi-domain, substrate-embedded, passive module, STILE™ is designed to support the growing number of power rails within the package.

www.sarasmicro.com

Our equipment enables advanced packages for high performance computing and AI applications.

Be it TGV for glass panels using TersOnus or fluxless solder reflow with VeroTherm FAR, YES offers a range of equipment for clean, coat, cure and wet processing that can accelerate your journey from Lab to Fab.

Call: +1 (510) 954-6889 (worldwide) or +1 (888) YES-3637 YES.tech

## Empowering the Future: New York's Semiconductor Surge in 2024

By Scott Sikorski, Ph.D., IBM

In 2024, New York's semiconductor industry experienced substantial growth, driven by increased funding from both the U.S. government and the expansion of IBM along with other key industry suppliers. As a result of these recent public and private initiatives, the NY CREATES' Albany NanoTech Complex—the largest non-profit semiconductor R&D facility of its kind in the nation—is expanding in size and capabilities.

This state-of-the-art facility has been instrumental for over two decades in fostering advancements in chip technology through collaboration among industry leaders, academic institutions, and international partners. The growth of the semiconductor sector in New York and throughout what is now referred to as the Northeast Corridor has been evident, with numerous announcements throughout 2024. Below is a summary of a portion of 2024's news from the region.

#### **Key 2024 New York Semiconductor Developments:**

#### **IBM Quantum System One Launch**

In April, Rensselaer Polytechnic Institute (RPI) and IBM unveiled the world's first IBM Quantum System One located on a university campus. This groundbreaking installation aims to enhance quantum computing research, workforce development, and educational initiatives in New York, further solidifying the partnership between RPI and IBM.

#### **ASMPT** and IBM Partnership Renewal

In July, ASMPT and IBM renewed their collaboration to advance chiplet packaging technologies. This partnership focuses on enhancing thermocompression and hybrid bonding techniques for chiplet packages, utilizing ASMPT's advanced Firebird TCB and Lithobolt hybrid bonding tools. This renewed effort builds on previous developments in hybrid bonding, aiming to create lighter, faster, and more energy-efficient semiconductor packaging solutions.

#### Investing in Next-Gen Chips Research

As part of the FY 2025 budget, New York State Governor Kathy Hochul secured a \$500 million capital investment for NY CREATES' Albany NanoTech Complex to jumpstart a \$10 billion partnership and bring a cuttingedge High NA EUV Lithography Center to the complex.

#### IBM Expansion at NY CREATES' Albany NanoTech Complex

In September, IBM announced plans to lease an additional 30,000 square feet at the Albany NanoTech Complex. This expansion is designed to accommodate a significant increase in the workforce, with plans to grow from 700 employees to between 850 and 999. The new agreement allows IBM to lease space in the ZEN building, which offers a total of 365,000 square feet, already fully occupied by IBM on its top floor.

#### Federal Funding for NORDTECH

Also in September, Governor Hochul celebrated the award of over \$30 million from the U.S. Department of Defense to support the NORDTECH research teams. This funding establishes the Northeast as a Department of Defense Innovation Hub and is intended to stimulate the development of a domestic microelectronics manufacturing industry. NORDTECH, formed in September 2023, is a regional coalition that includes key institutions like NY CREATES, the University at Albany, Cornell University, RPI, and IBM, all focused on creating a pathway from research ("lab") to production ("fab").

#### **NSF Grant for Workforce Development**

On September 30, NY CREATES announced it received a \$4.7 million grant from the National Science Foundation to launch a Semiconductor Workforce Development Program. Senate Majority Leader Charles Schumer emphasized that this funding, part of the CHIPS & Science Act will provide college students nationwide with hands-on training at Albany NanoTech, preparing them for careers in the semiconductor industry.

Overall, these initiatives highlight New York's strategic position as a key player in the semiconductor landscape, driving innovation and workforce development in this critical field. IBM is proud to play a crucial role in this growth, supported by our world-class labs and manufacturing facilities in Albany, Yorktown Heights, the mid-Hudson Valley, and other parts of the thriving Northeast Corridor.

#### **Asia May Still Be the Hottest Spot for Advanced Packaging**

By Dean Freeman, Freeman Technology and Market Advisors

When the United States and Europe looked to reshore semiconductor technology, the primary focus was restoring leading-edge manufacturing and creating more resilient supply chains throughout the ecosystem. Eventually, it emerged that nearly all of the leading-edge packaging took place overseas, and there was minimal packaging capability in either the U.S. or Europe.

This should not come as a surprise to anyone involved in the industry. Almost as soon as the semiconductor industry started manufacturing chips; test, assembly, and packaging were moved offshore, as it was considered more economical to perform those tasks overseas. This trend led to strong growth of outsourced semiconductor assembly and test service (OSATs) providers and integrated device manufacturer (IDM) packaging across the Asia Pacific (AP) region.

The Asia Times wrote that advanced packaging is the next front in the chip wars. If you think that conquest or success in war arises from how much territory, or in this case manufacturing is performed in Asia, then this will be a long-drawn-out battle where the Asia Pacific region already has most of the territory. When the U.S. Department of Commerce (DOC) was preparing the arguments for the CHIPS Act, it was determined that only 3% of the packaging occurred in the U.S., and of that very little advanced packaging when the report was first written.

While the U.S. is attempting to recover some of that packaging share, the real hotspot for packaging is in the Asia Pacific Region. The market can be broken up into the semiconductor fabs that also do advanced packaging either for themselves or foundry partners and the OSAT companies, which are essentially the

packaging and test foundries for the majority of the industry. SEMI is tracking over 500 OSAT providers and 170 IDM facilities. As the graph shows the majority of these packaging facilities are in the Asia Pacific region.

## Worldwide Assembly & Test Facilities 160

Figure 1: Worldwide Assembly and Test Facilities (Source: SEMI)

Companies manufacturing chips, both IDM and foundry, provide a considerable amount of packaging services in the AP region. The foundry operations of Samsung and TSMC have significant packaging capacity and are adding more as demand for chiplets to support Al capacity for their partners. Chiplets are also finding their way into phones, automotive, and PCs, which is increasing the demand for chiplet capacity to which the OSATs are responding in partnership with fabs and foundries.

Samsung, Hynix, and Micron perform most of their memory packaging in the AP region. Samsung and Hynix are packaging mostly in Korea with some manufacturing occurring in China. Micron has facilities in Singapore, Malaysia, China, and Taiwan. Micron is also expanding to India with a new facility expected to open in 2025. Intel has packaging and assembly facilities in Malaysia, China, and Vietnam in addition to its U.S. efforts.

**CAMERA MODULE ADHESIVES**

**CAPILLARY UNDERFILLS**  **STRETCHABLE INKS**

**BOARD-LEVEL MATERIALS**

LIQUID **COMPRESSION** MOLDING

**SINTERING TECHNOLOGY**

Scan to get in touch with a NAMICS sales representative

our sintering materials

NAMICS Technologies, Inc.

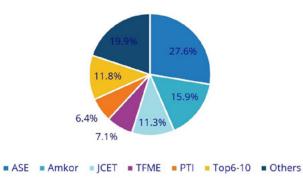

OSATs makes up the bulk of the packaging resources for the semiconductor industry. Most of these facilities are located in the AP region, with China and Taiwan having over half of the OSAT facilities and revenue across the industry. According to IDC, the top 10 OSAT companies are responsible for over 80% of the industry's revenue, with ASE and Amkor, the top 2 OSAT companies, accounting for over 40% market share. The top 10 OSATs are located primarily in Taiwan and China, with one in Singapore. The OSATs have facilities spread throughout the AP region, for example, Amkor has packaging facilities in Taiwan, China, Korea, Japan, Malaysia, Vietnam, and the Philippines.

- 1. ASE Group: Headquarters Taiwan

- Amkor: Headquarters U.S., Manufacturing mostly AP

- 3. Powertech Technology Inc: Headquarters Taiwan

- 4. Chipmos Technologies: Headquarters Taiwan

- 5. **King Yuan Electronics Co. Ltd:** Headquarters Taiwan

- 6. Formosa Advanced Technologies: Headquarters Taiwan

- 7. **JCET:** Headquarters China

- 8. UTAC Holdings Ltd: Headquarters Singapore

- 9. Lingsen Precision Industries Ltd: Headquarters Taiwan

- 10. Tongfu Microelectronics Co.: Headquarters China

#### Worldwide Top 10 OSAT Companies, 2022 Market Share

Figure 2: Worldwide Top 10 OSAT companies, 2024 market share. (Source: IDC)  $\,$

With all of the chiplet noise in the marketplace, one might think that most of the chiplet development occurs either at TSMC in Taiwan or at Intel in the U.S. This is far from the case. A considerable amount of chiplet devices are assembled and packaged at the OSATs. AMD has partnered with Tongfu Micro to handle its chiplet packaging. Tongfu and AMD co-developed their chiplet capability in 2017 when AMD first started chiplet development. Intel's Embedded Multi-die Interconnect Bridge (EMIB) packaging, which is considered 2.5D, is done in Malaysia as well. Foveros is packaged in the U.S. at the moment, but that may also be outsourced to AP.

Samsung has a considerable 3D packaging effort for its advanced logic foundry partners, Samsung Advanced Logic, and HBM located in Korea. SK Hynix performs most of its HBM packaging and development in Korea as well. All the memory companies are partnering with TSMC, or other OSATs to get their HBM integrated into advanced packages.

OSATs are a big part of the 3D ecosystem, an most packaging development happens at these companies. ASE has long partnered with TSMC and got a shout-out at TSMC's North America OIP presentations. Amkor is also moving forward with TSMC in Arizona for 3D packaging technology.

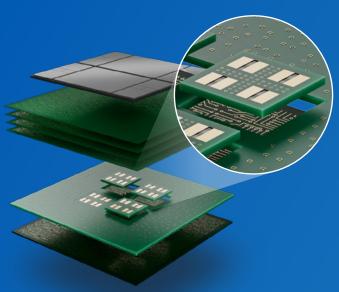

Panel-level packaging (PLP) is a hot new technology for chiplet manufacturing. Wafer-level packaging (WLP) cannot support the volume of chiplet devices needed by the microelectronics industry. The industry is shifting from using wafers or round substrates to glass panels. <a href="Innoluxin Taiwan">Innolux in Taiwan</a> is operating a 3.5G panel-level packaging plant. TSMC just purchased a 5.5G flat panel factory for the same purpose and <a href="Micron has been looking at several flat panel facilities">Micron has been looking at several flat panel facilities</a> for PLP. TSMC expects to have a 9-reticle package in production by 2027.

Figure 3: Panel level packaging panel dimensions (Source: Innolux)

Advanced packaging will continue to be an area of strong growth for the industry. In a recent earnings call, CC Wei, CEO of TSMC, mentioned that in 2023, the foundry business was about \$117 billion; however, with the addition of advanced packaging to TSMC's and other companies' product lines, the foundry business was estimated to be 250 billion dollars. That's a doubling of the foundry market and is mostly due to advanced packaging.

With a market size of over \$100 billion and no signs of the AP region slowing down in the packaging market, AP will continue to be the hot spot for advanced packaging for some time to come.

## **US-JOINT Consortium: Strengthening Advanced Packaging Innovation Across Borders**

By Avery Gerber

As global semiconductor demand continues to surge, international collaboration has become essential for driving technological innovation. The US-JOINT consortium represents a key initiative in fostering cross-border cooperation between Japan and the United States. This groundbreaking collaboration brings together 10 companies- Azimuth Industrial Co. Inc., KLA Corp., Kulicke & Soffa Industries Inc., TOWA Corp., ULVAC Inc., Moses Lake Industries Inc., MEC Co. Ltd., NAMICS Corp., Tokyo Ohka Kogyo Co. Ltd., and Resonac Corp. to work on advanced semiconductor packaging research and development. Three of these companies—KNS, NAMICS, and KLA—are members of the 3D InCites community.

In response to the growing need for sophisticated packaging solutions, the US-JOINT consortium aims to leverage the unique strengths of its participants in both countries. I spoke with several key members, including Kazuyuki Mitsukura, the technical director leading US-JOINT at Resonac America, to learn more about the initiative's goals. We also spoke with representatives from KLA, Kulicke & Soffa, and NAMICS.